1. 功能描述

架构与指令集

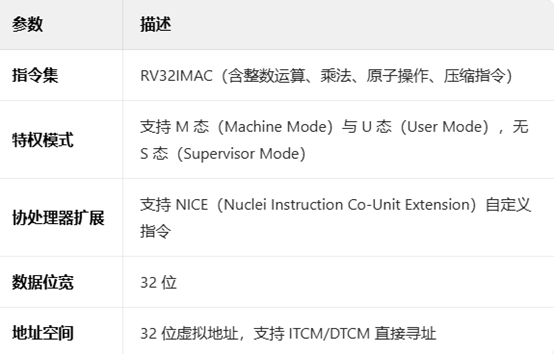

指令集:支持 RV32IMAC 指令集(整数运算、乘法 / 除法、原子操作、压缩指令),兼容 RISC-V 基线标准。

流水线:极简 2 级流水线(取指、执行),降低设计复杂度和面积,适合低功耗场景。

特权模式:支持机器模式(Machine Mode, M 态),满足嵌入式系统基础安全与资源管理需求。

性能与功耗

面积:仅 0.015mm²(65nm工艺),适合对面积敏感的 IoT 设备。

功耗:极低动态功耗设计,典型运行功耗低于 100μW,支持睡眠模式进一步降低静态功耗。

处理能力:最高主频可达 200MHz(视工艺而定),CoreMark 评分约200 分,满足轻量级计算任务。

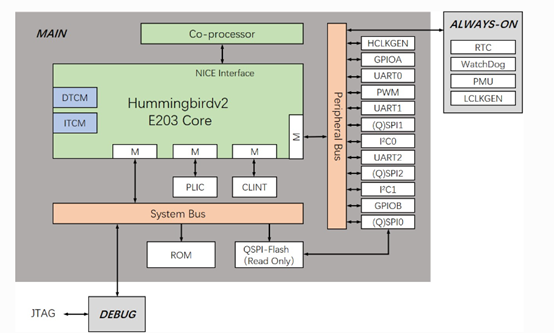

外设与接口

总线接口:支持自定义轻量级总线(如 AXI4-Lite、Wishbone),便于SoC 集成。

调试接口:集成 RISC-V 标准调试模块(Debug Module),支持JTAG/SWD 调试,兼容 GDB 工具链。

可扩展性:预留自定义扩展接口(如中断控制器、定时器、GPIO),方便添加专用硬件加速模块。

应用场景

物联网终端:传感器节点、智能家电、穿戴设备(如华米“黄山1号”芯片基于此架构)。

嵌入式控制:工业控制、电机驱动、低功耗 MCU。

2. E203 蜂鸟可交付清单

开源代码与设计资源

RTL 代码:完整Verilog 源码(Apache 2.0 协议),包含处理器内核、调试模块、总线接口等。

SoC 参考设计:基于E203 的最小系统集成方案(如时钟、复位、内存控制器),支持 FPGA 验证(如 Xilinx Artix-7 开发板)。

测试平台:包含仿真测试用例(UVM 验证环境),覆盖指令集功能、时序及边界条件测试。

工具链与开发套件

编译工具链:开源 RISC-V GCC 工具链(支持交叉编译),配套 Makefile 和构建脚本。

调试工具:GDB 调试脚本、OpenOCD 配置文件,支持 JTAG/SWD 硬件调试。

集成开发环境(IDE):适配Eclipse 的 Nuclei Studio(含代码编辑器、调试器、性能分析工具)。

文档与技术资料

架构手册:详细说明指令集实现、流水线结构、寄存器定义及异常处理机制。

用户指南:SoC 集成步骤、外设驱动开发示例、功耗优化建议。

开源协议:Apache 2.0 许可证全文,明确商业使用与修改权限。

生态与支持

示例工程:包含 UART 通信、GPIO 控制、定时器中断等基础功能 Demo,及 RT-Thread/FreeRTOS 操作系统移植案例。

社区资源:芯来科技官方论坛、RISC-V 中国社区技术支持,定期更新补丁与优化版本。

教育资源:配套实验指导书、高校课程教案,支持芯片设计入门教学。

3. 示意图

4. 技术规格或参数