1.简介

逐次逼近型模数转换器(Successive Approximation Register ADC,SAR ADC)是一种通过逐次比较实现模拟信号数字化的高精度转换器。其核心工作原理基于二分法搜索:初始化时,SAR逻辑设定最高位(MSB)为1,其余位为0,通过内部数模转换器(DAC)生成对应模拟电压,与输入信号比较。若DAC输出高于输入,则该位复位为0;反之保留为1。此过程逐次迭代至最低位(LSB),最终输出数字码。

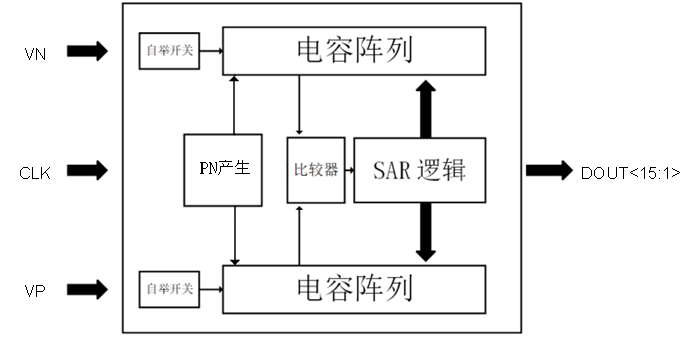

2.关键结构组件

采样保持电路(S/H):确保转换期间输入信号稳定。

比较器:执行模拟电压的实时比较。

电容阵列DAC:将数字码转换为精确的模拟参考电压。

SAR控制逻辑:管理逐次逼近的时序与决策流程。

时钟模块:同步各环节操作。

采样率:50MS/s

校准后有效位数(ENOB)=9.5bit

校准后信噪失真比(SNDR)=58.51dB

校准后无杂散动态范围(SFDR)=76.81dB