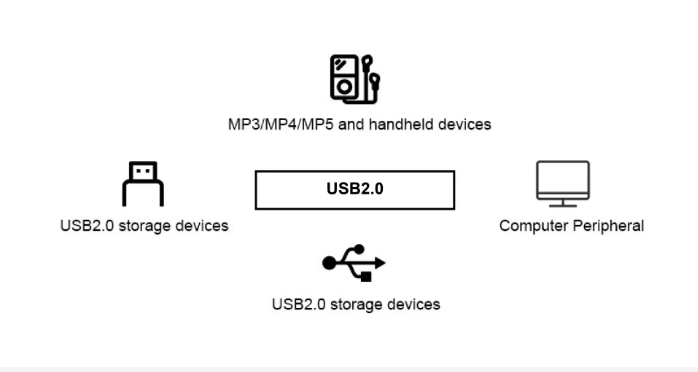

该IP USB 2.0 PHY 符合 UTMI+ Level 3 Revision 1.0(USB 2.0 Transceiver Macrocell Interface Plus)的规范,性能卓越。作为一款集成高速混合信号电路,该IP USB 2.0 PHY 不仅支持 1.5Mbps 的 LowSpeed (LS) 和 12Mbps 的FullSpeed (FS),还支持 480Mbps 的HighSpeed (HS) ,同时保留与 USB1.1 Legacy 的向后兼容性。

该IP USB 2.0 PHY 能够处理低级协议和信号传输。在 TX 模式下,PHY 对数据进行串行化,根据需要进行 NRZI 编码和 bit 填充,然后生成 SYNC 和 EOP 字段。同样,在 RX 模式下,它从传入数据中恢复时钟,剥离 SYNC 和 EOP 字段,根据需要进行 NRZI 解码和 bit 去填充,然后对数据进行反串行化。它支持 LS、FS、HS、On-The-Go (OTG)、Device 和 Host 等 17 种操作模式。

该IP USB 2.0 PHY 可预配置 30MHz 16 位或 60MHz 8 位 UTMI 的数据接口,提供具有 ESD 保护的完整片上 Transceiver 物理解决方案。

eUSB2 IP 支持 Native 模式和 Repeater 模式,使应用更加灵活。 eUSB2 Repeater 在标准 USB 2.0 和 eUSB2 信号电平之间进行转换,允许 Legacy USB 2.0 设备连接到带有 eUSB2 PHY 的系统级芯片 (SoC)。基于多年客户成功经验,该IP提供经过硅验证的可定制化 eUSB2 PHY,完全符合 USB-Implementers Forum 的(USB-IF) eUSB2 和 USB 2.0 规范。

低功耗

完全可定制

高速 Hub, VLPI 低延迟

面积小

易集成

可选服务包括

测试芯片和测试板

FPGA 集成支持

芯片级集成

符合 USB Specification Revision 2.0, 1.1

支持 8 位或 16 位 UTMI 接口,符合 UTMI+ Specification Level 3 Revision 1.0

符合 OTG Supplement to the USB Specification Revision 2.0(可选)

支持 480Mbps (HS)、12Mbps (FS) 和 1.5Mbps (LS) 串行数据传输

支持低延迟 Hub 模式,具有 40-bit 延迟

支持 USB Specification Revision2.0 中定义的所有测试模式

支持 Scan 和 Loopback BIST 模式

内置 I/O 和 ESD 结构

片上自校准 HS/FS/LS 终端

支持 12/19.2/20/24MHz 外部晶振或片上参考时钟,带有 PLL 振荡器

嵌入式 ESD 电路,HBM 为 2000V,CDM 为 500V

数据手册和物理实施指南

库交换格式 (LEF) 文件

门级网表和标准延迟格式 (SDF) 时序文件

加密的 Verilog 模型

布局与原理图 (LVS) 扁平网表和报告

设计规则检查 (DRC) 报告

用于 Foundry merge 的 GDSII 数据库

测试芯片和 FPGA 支持(可选)

后端集成(可选)