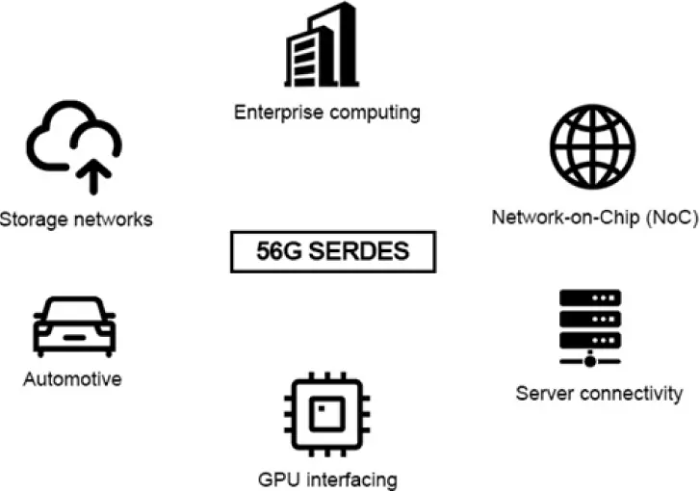

该IP 56G SerDes PHY 是一款灵活性极高的 PHY,单通道速率高达 56Gbps,支持 56G PAM-4 和 NRZ,同时,可通过调整 PCS 层和寄存器配置支持各种高速 SerDes 协议。

这款硬核 PHY 设计精良,符合 IEEE 和 OIF 协议,具备稳健的 ESD 结构和 BIST 功能。该 IP 支持芯片、光学器件和背板之间的高速互连,内置低抖动 LC PLL 和 CDR,优化信号完整性。该IP 56G 长距离 SerDes 解决方案在功率、性能和面积等方面表现出色,能够完美适应各种网络应用需求。它不仅提供高效的互连性能,还兼具低功耗和紧凑设计,是实现高性能网络系统的理想选择。

PHY 完全符合以下标准:PCIE6/5、IEEE 802.3 和 OIF、CEI-56G+ LR PAM-4、CEI-25G+ LR/MR NRZ、JESD204C/B (25/32G)、10GKR/100G KR-4 LR、400GAUI-8 LR/MR、CEI11G-LR。

提供领先的性能、功率和每Tb面积

可选 PI/SI 和热协同设计服务

从 IP 交付到生产的全面支持

符合 IEEE 802.3 和 OIF 标准和电气规范

64/56Gbps 串行数据速率,支持 28-32G VSR/SR/MR/LR NRZ 和 64/56G PAM-4

支持高达 -36dB 插入损耗 @14GHz

支持 100/156.25MHz 参考时钟,由外部或芯片内提供

嵌入式高精度低抖动 LC PLL 和 CDR

85欧姆差分片上端接 Driver 和 Receiver,具有自动阻抗校准功能

多种 BIST 模式和 Test pattern generation

支持近端串行 Loopback 和远端并行 Loopback

专有低电容 ESD 结构

片上 PRBS 生成和验证,由外部终端控制

调校良好的 IO 和封装模型,实现优异的信号完整性和性能

数据手册和详细的物理实施指南

完整的时序模型

库交换格式 (LEF)

加密 Verilog 模型

版图与原理图 (LVS) 报告

GDSII 数据库