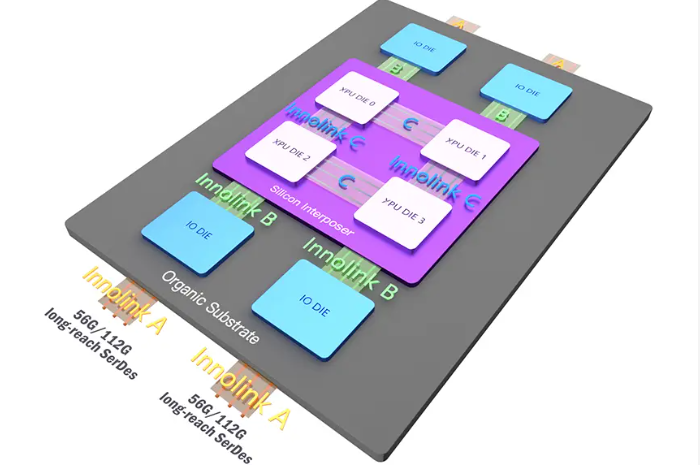

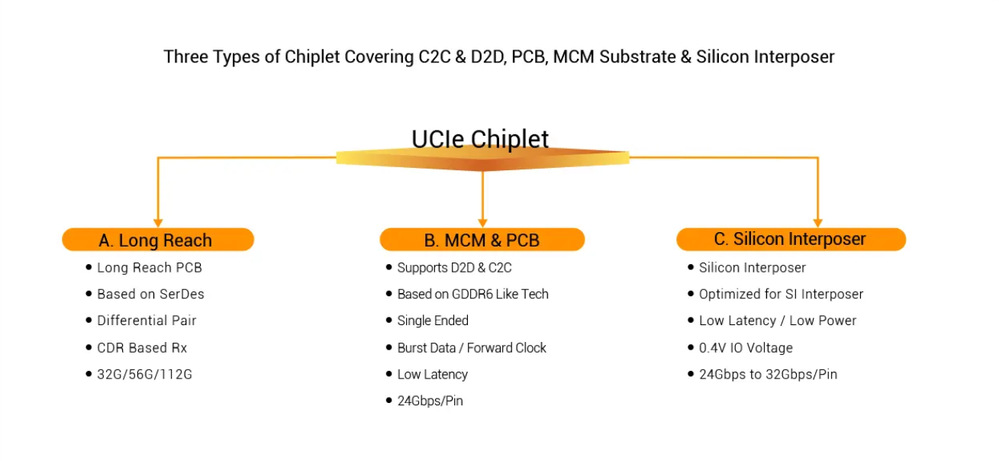

该IP UCIe Chiplet IP 提供先进的 Chiplet 解决方案,使大量低延迟数据能够像在同一条总线上一样,在较小芯片之间无缝传输。Chiplet 是指组成大芯片的独立功能块,在异构集成时代实现性能和效率提升中具有关键作用。这一解决方案在数据中心、网络、5G、高性能计算(HPC)和人工智能(AI)应用中,是实现高效低成本的裸片到裸片 (Die-to-Die,D2D)、芯片到芯片 (Chip-to-Chip,C2C)、板到板 (Board-to-Board,B2B) 和封装到封装 (Package-to-Package,P2P) 连接的关键推动力。

支持最新的 UCIE 1.1 版本

结构灵活,易于定制(预设计的硬核 PHY 支持客户定制、PHY + 适配层、PHY + 适配层 + 定制协议层)

支持使用 Streaming 封装的 CXS/AXI(AXI 接口带宽最高可达 89%)

支持 CXL/PCIE 接口

容错机制:支持 CRC + Retry + FEC

支持 FEC 机制(可选)

低功耗:支持驱动/接收强度调整和自动时钟门控(时钟门控比 > 95%)

完整的 DFX 调试机制

支持性能监视器(带宽宽度/延迟监视和事件监视)

支持完整的 BIST 和 On Die Scope 机制(覆盖协议层到链路层)

支持 MCM、INFO 和 Interposer 封装以及 PCB

高性能:MCM 上高达 24Gbps,PCB上高达 20Gbps

自动跟踪:正向时钟,支持 PVT 自动跟踪

低延迟:链路层延迟低于 3ns

PHY 层全面 training

高密度:标准 Pitch 和 Micro Bump

数据手册和物理实施指南

网表(用于LVS 的 Spice 格式)

库交换格式 (LEF)

Verilog 模型

GDSII 到 Foundry IP 合并

模块集成指南

带驱动程序和 ODT 调整的 WCK/DQ/DV/DX IBIS 模型

硅片验证报告(可用时)

评估板(可用时)

数据手册、应用说明

Verilog Getech 文件

SDC 文件

仿真环境和用户指南