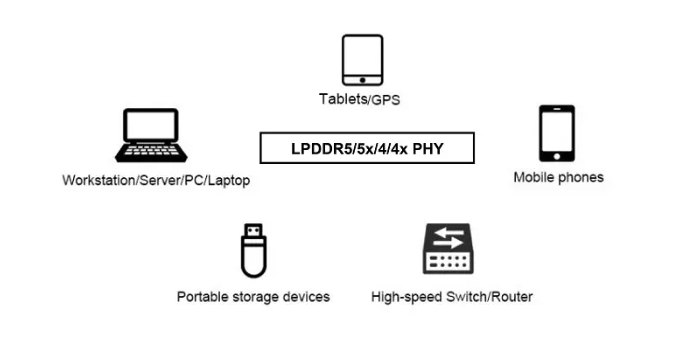

该IPDDR混合信号 IP,LPDDR5/5x/4/4x PHY 和控制器,为 IC 设计提供一站式物理接口解决方案。该 IP 兼容 JEDEC 标准,支持所有市场上的 LPDDR5/5x/4/4x SDRAM 组件。针对低功耗和高速应用进行优化,具备稳健的时序特性和较小的硅片面积。DDR PHY 组件包含 DDR 专用高性能 I/O、关键时序同步模块 (TSM) 以及具有可编程精细粒度控制的低功耗、低抖动 DLL,以支持上述 DDR 设备接口。

预先设计好的硬核IP可简化集成并并缩短设计周期

稳健的 ESD 架构,零风险

在 VDD 掉电期间保持自刷新前的 I/O 驱动状态

广泛支持各种EDA设计工具和流程

支持 DFI4.0/4.1/5.0 内存控制器接口

充分发挥和利用各种工艺节点的速度和功耗优势

一流的低噪声设计,确保最佳时序裕度和信号完整性

DFT 功能可缩短测试时间并确保高测试覆盖率

通过简单的寄存器接口实现多种 PHY 模式配置

每个 IO 都自带可调的延时功能,以保证高速工作时能够获得最佳的眼图采样位置

支持 LPDDR5/5x 和 LPDDR4/4x 模式和信号,速率分别为 20Mbps 至 9600Mbps (LPDDR5x)、6400Mbps (LPDDR5) 和 4266Mbps (LPDDR4/4x)

支持 x16/x32/x64 数据位宽

支持 JEDEC LPDDR4/4x 1.1V/0.6V 和 LPDDR5 0.5V/0.3V LVSTL IO 电压

支持 LPDDR5 WCK 模式、Data copy、Write X 和Link ECC 功能

独立读写时序调整,支持自动校准

可配置的 Write post-amble(0.5 tCK 或 1.5 tCK)

支持 PoP 和分立存储器封装

支持定制的硅信号和 PG bump,以优化封装设计。

支持各种低功耗模式,支持 DFS 和 Retention 模式

支持单 Rank 和多 Rank 配置

支持 PVT 补偿和时序校准,确保所有 corner 的可靠性

支持 At-speed BIST、Scan Insertion、PAD 和 Internal Loopback 模式

支持各种低功耗模式,包括自刷新时的 core 电源掉电

低抖动,具有出色的噪声抑制

支持 APB 寄存器接口

使用 RVT&LVT&ULVT 核心设备和标准技术 IO 设备实现

支持 Wire-bond 和 Flip-chip 封装

支持不同类型的 DDR 信号映射,方便 PCB 布局

Verilog 模型

LEF

布局布线 abstracts

GDSII 文件

LVS 网表

IO 的 HSPICE 仿真网表或 IBIS I/O 模型(可选)

数据手册、应用说明

硅片验证和 ESD 测试结果

PCB 参考设计和封装电气模型(可选)